#### **PRODUCT BRIEF > OPTICAL**

# **Optical DSP** Lark 850

### 800Gbps TX Only DSP (8:8)

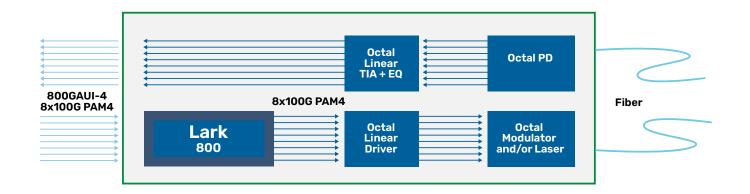

The Lark 850 is a uni-directional 8 x 112Gb/s Digital Signal Processor (DSP) IC that is optimized for Linear Receive Optics (LRO). In an LRO transceiver or Active Optical Cable (AOC), only the transmit path from the electrical input to the optical line side output includes a DSP for signal retiming and equalization.

As hyperscale data center AI deployments grow rapidly, high-speed optical transceivers and AOCs are critical to connecting thousands of GPUs. Given the huge volume of these optical components, improvements in energy efficiency are essential. Lark 850 reduces DSP power by 50% and optimizes cost while providing customers with an easy to use, robust, and interoperable solution. Transceiver vendors can further optimize the module cost with Lark 850 by employing a variety of optics, including VCSELs, silicon photonics, EML or thin-film lithium niobate as dictated by the application requirements.

A Lark 850 based optical transceiver addresses the inherent weakness of a Linear Pluggable Optics (LPO) implementation by facilitating IEEE compliant optical transmit signaling and easing the deployment burden on system operators by eliminating manual, per port tuning. The result is lower bit error rates, enhanced sensitivity, reduced performance variation, and improved resilience to different switch ASICs, PCB traces, optical components, and environmental conditions.

The Lark 850 features independent PLL's for each lane to support breakout applications, an OIF CEI-112G-MR compliant host interface, and numerous integrated diagnostic features to accelerate time to market and aid with system debug.

#### **Applications**

- · Hyperscale data centers

- · Cloud and AI networks

- 800GbE optical transceivers and A0Cs

- 2x400GbE optical transceivers and AOCs

- Breakout applications

### **Key Parameters**

| Host Side             | 8x106G PAM4 |

|-----------------------|-------------|

| Line Side             | 8x106G PAM4 |

| <b>Operating Temp</b> | 0° to 85°C  |

#### **Key Features**

- Powerful copper optimized DSPs on the electrical host side deliver industry leading sensitivity and BER performance.

- High-performance transmitters come with multi-tap FIR filters and non-linear cancellation, allowing precision optimization at the optical interface.

- Host side interface supports VSR or extended MR PCB reach, connecting seamlessly with different length switch interfaces without need for customized per-channel settings.

- Independent phase locked loops per channel support flexible breakout configurations including 2x400GbE, 4x200GbE and 8x100GbE.

- Full suite of test features simplifies lab bring-up, production testing and reduces time-to-market.

- Low power dissipation enables higher rack utilization and lower thermal cooling requirements.

## Supported Standards and Interfaces

- 800G-SR8/DR8/FR8/LR8

- 2x400G-SR4/DR4/FR4/LR4

- 4x200G-SR2/DR2/FR2/LR2

- 8x100G-SR/DR/FR/LR

- 100GAUI-1, 400GAUI-4, 800GAUI-8

- OSFP and QSFP-DD800

- CMIS 4.x and 5.x

### **About Credo**

Credo's mission is to advance high-speed connectivity solutions that deliver optimized performance, reliability, energy efficiency, and security for the next generation of AI driven applications, cloud computing, and hyperscale networks.

Optimized for both optical and electrical applications, our solutions support port speeds up to 1.6Tb. At the core of our technology is our proprietary Serializer/Deserializer (SerDes) IP. Our diverse solutions portfolio includes system-level products such as Active Electrical Cables (AECs), a range of Integrated Circuits, including Retimers, Optical DSPs, SerDes chipsets, and SerDes IP Licensing.

# For more information please visit www.credosemi.com or email sales@credosemi.com

© 2025 Credo Semiconductor, Inc. All Rights Reserved. Credo Semiconductor Inc. and the Credo logo are trademarks of Credo Semiconductor Inc. All other marks are the property of their respective owners. This document is for information only. Specifications are subject to change without notice.

REV 031225