#### **AEC SPAN SPECIFICATION**

## **Plug & Play Active Electrical Cable** for Rack to Rack Ethernet Applications

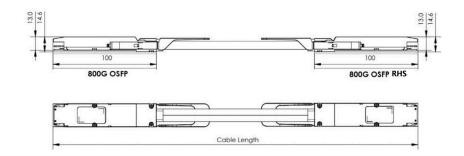

### 800G OSFP to 800G OSFP-RHS

#### Credo's ZeroFlap Family of HiWire™ SPAN Active Electrical Cable

A 800G AEC specifically designed for rack-to-rack connectivity, support up to 7 m reach, consume up to 50% less power than optical and take 75% less volume than DACs, and offer a 10-year service life.

With improved reach and signal integrity, these AECs deliver zero soft link flaps to support the lossless backend RDMA network that AI clusters are built on. With advances in liquid cooling, the 7 m length enables the full host to switch connectivity for leading GPU clusters.

#### Credo's CAC8XXXX1A1B-C1-HW HiWire AEC

Designed to deliver highly reliable interconnect for artificial intelligence (AI) backend networks. It can sustain 8 lanes of 100G PAM4 signal in each direction, providing bi-directional 800Gbps traffic per cable. The use and replacement of CAC8XXXX1A1B-C1-HW AEC is simple and straightforward as it adopts standard OSFP form factor and complies to MSA specifications.

#### **Features**

The following are the key features of the HiWire SPAN AEC:

- Recognizable, purple PET braided jacket

- 800G to 800G data rate

- CMIS 5.1 compliant

- Single 3.3V power supply

- Low power consumption: Typically 10W power dissipation each end

- BER<10<sup>-15</sup> (post FEC)

- Hot pluggable

- RoHS2 compliant

- I<sup>2</sup>C management interface

- Operating case temperature range: 0 to +70°C

## Supported Standards and Interfaces

- Common Management Interface Specification (CMIS) v5.1

- OSFP MSA v3.0

## **Key Features**

| Parameter                        | Value                             |

|----------------------------------|-----------------------------------|

| Module Form Factor               | OSFP to OSFP-RHS                  |

| Number of Data Lanes             | 8 TX and 8 RX per module (PAM4)   |

| Maximum Aggregate Data Rate      | 800Gbps                           |

| Nominal Data Rate per Lane       | 106.25Gbps (PAM4)                 |

| Electrical Interface and Pin-out | 60-pin edge connector             |

| Pin Description                  | Per OSFP hardware specification   |

| Management Interface             | I²C, serial, timing per CMIS v5.1 |

| Length of Copper AEC             | 3.0m - 7.0m                       |

| BER (Pre-FEC)*                   | Тур. <10-8                        |

| BER (Post-FEC)*                  | <10 <sup>-15</sup>                |

\* Tested with QPRBS31 pattern

## **Product Selections**

| Part Number        | Length |

|--------------------|--------|

| CAC83X301A1B-C1-HW | 3.0m   |

| CAC835301A1B-C1-HW | 3.5m   |

| CAC84X301A1B-C1-HW | 4.0m   |

| CAC845301A1B-C1-HW | 4.5m   |

| CAC85X301A1B-C1-HW | 5.0m   |

| CAC855281A1B-C1-HW | 5.5m   |

| CAC86X281A1B-C1-HW | 6.0m   |

| CAC865281A1B-C1-HW | 6.5m   |

| CAC87X281A1B-C1-HW | 7.0m   |

# For more information please visit **www.credosemi.com** or email **sales@credosemi.com**

© 2024 Credo Semiconductor, Inc. All Rights Reserved. Credo Semiconductor Inc. and the Credo logo are trademarks of Credo Semiconductor Inc. All other marks are the property of their respective owners. This document is for information only. Specifications are subject to change without notice. REV 100924