SHIFT AEC SPECIFICATION

# for Speed Shifting Ethernet Applications

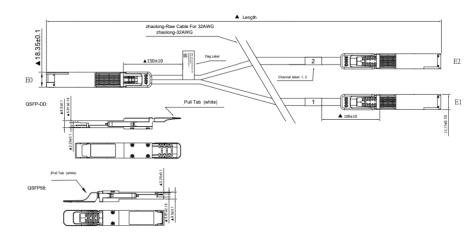

400G QSFP-DD to 2x200G QSFP56

is a lower power, lower cost solution to Active Optical Cable (AOC) transceiver solutions for high speed interconnect (up to 400Gbps). Powered by Credo's best-in-class signal processing technology, this Plug & Play cable provides connectivity between PAM4 Q56 4 lane and 2 lane ports over thin copper cables without using any optical components and consumer up to 50% less power than optics.

With improved reach and signal integrity, these AECs deliver zero soft link flaps to support the lossless backend RDMA network that AI clusters are built on. The ZeroFlap AEC enables the full host to switch connectivity for leading GPU clusters

Designed for telecom and data center use. The 400G cable breaks out from one 400G (8x56G-PAM4) QSFP56 end into two 200G (4x56G-PAM4) QSFP56 ends. The use and replacement of ZeroFlap SHIFT AEC is simple and straightforward as it adopts standard QSFP form factors and complies to MSA specifications.

### **Applications**

- Recognizable purple mesh jacket

- 400G to 2x200G with breakout function

- · 400G CMIS4 / 200G SFF-8636

- · Single 3.3V power supply

- Low power consumption:

Typ. 4.5W power

- dissipation (QSFP-DD)

- Typ. 2.5W power dissipation(QSFP56)

- BER < 10^-15 (post FEC)</li>

- · Hot pluggable

- · RoHS2 compliant

- · I2C management interface

- Operating case temperature range: 0 to +70°C

## Supported Standards and Interfaces

- Common Management Interface

Specification v4.0

- SFF-8636 QSFP56 Electrical Specification

#### **Key Features**

| Parameter                        | Value                                                                             |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------|--|--|--|

| Module Form Factor               | QSFP-DD and QSFP56                                                                |  |  |  |

| Number of Data Lanes             | QSFP-DD 8 TX and 8 RX per Module (PAM4)                                           |  |  |  |

|                                  | QSFP56 4 TX and 4 RX per module (PAM4)                                            |  |  |  |

| Maximum Aggregate Data Rate      | 400Gbps                                                                           |  |  |  |

| Nominal Data Rate per Lane       | QSFP-DD: 56Gbps (PAM4)                                                            |  |  |  |

|                                  | QSFP-56: 56Gbps (PAM4)                                                            |  |  |  |

| Electrical Interface and Pin-out | 76-pin edge connector (QSFP-DD) and 38-pin edge connector (QSFP56)                |  |  |  |

| Pin Description                  | Per QSFP-DD Hardware Specification (QSFP-DD)                                      |  |  |  |

|                                  | Per SFF-8636 (QSFP56)                                                             |  |  |  |

| Management Interface             | I2C, serial, timing per Common Management                                         |  |  |  |

|                                  | Interface Specification for 8X/16X Pluggable                                      |  |  |  |

|                                  | Transceivers (QSFP-DD) 12C, serial, timing per SFF-8636 (QSFP56 SFF-8636 version) |  |  |  |

|                                  |                                                                                   |  |  |  |

|                                  |                                                                                   |  |  |  |

| Length of Copper AEC             | 1.0m - 3m, 5m                                                                     |  |  |  |

| BER (Pre-FEC)*                   | Typ. <10 <sup>-8</sup>                                                            |  |  |  |

| BER (Post-FEC)*                  | <10:15                                                                            |  |  |  |

<sup>\*</sup> Tested with QPRBS31 pattern

#### **Product Selections**

| Part Number        | Length | Tolerance     | CMIS     | Weight |

|--------------------|--------|---------------|----------|--------|

| CAC41X321D2Q-D1-HW | 1.0m   | <u>+</u> 50mm | CMIS 4.0 | 220g   |

| CAC415321D2Q-D1-HW | 1.5m   | <u>+</u> 50mm | CMIS 4.0 | 260g   |

| CAC42X321D2Q-D1-HW | 2.0m   | <u>+</u> 50mm | CMIS 4.0 | 300g   |

| CAC425321D2Q-D1-HW | 2.5m   | <u>+</u> 50mm | CMIS 4.0 | 360g   |

| CAC43X321D2Q-D1-HW | 3.0m   | <u>+</u> 50mm | CMIS 4.0 | 420g   |

| CAC45X301D2Q-D1-HW | 5.0m   | <u>+</u> 50mm | CMIS 4.0 | 660g   |

#### **About Credo**

Credo's mission is to advance high-speed connectivity solutions that deliver optimized performance, reliability, energy efficiency, and security for the next generation of Al driven applications, cloud computing, and hyperscale networks. Optimized for both optical and electrical applications, our solutions support port speeds up to 1.6Tb. At the core of our technology is our proprietary Serializer/Deserializer (SerDes) IP. Our diverse solutions portfolio includes system-level products such as Active Electrical Cables (AECs), a range of Integrated Circuits, including Retimers, Optical DSPs, SerDes chipsets, and SerDes IP Licensing.

For more information please visit www.credosemi.com or email sales@credosemi.com