01

02

03

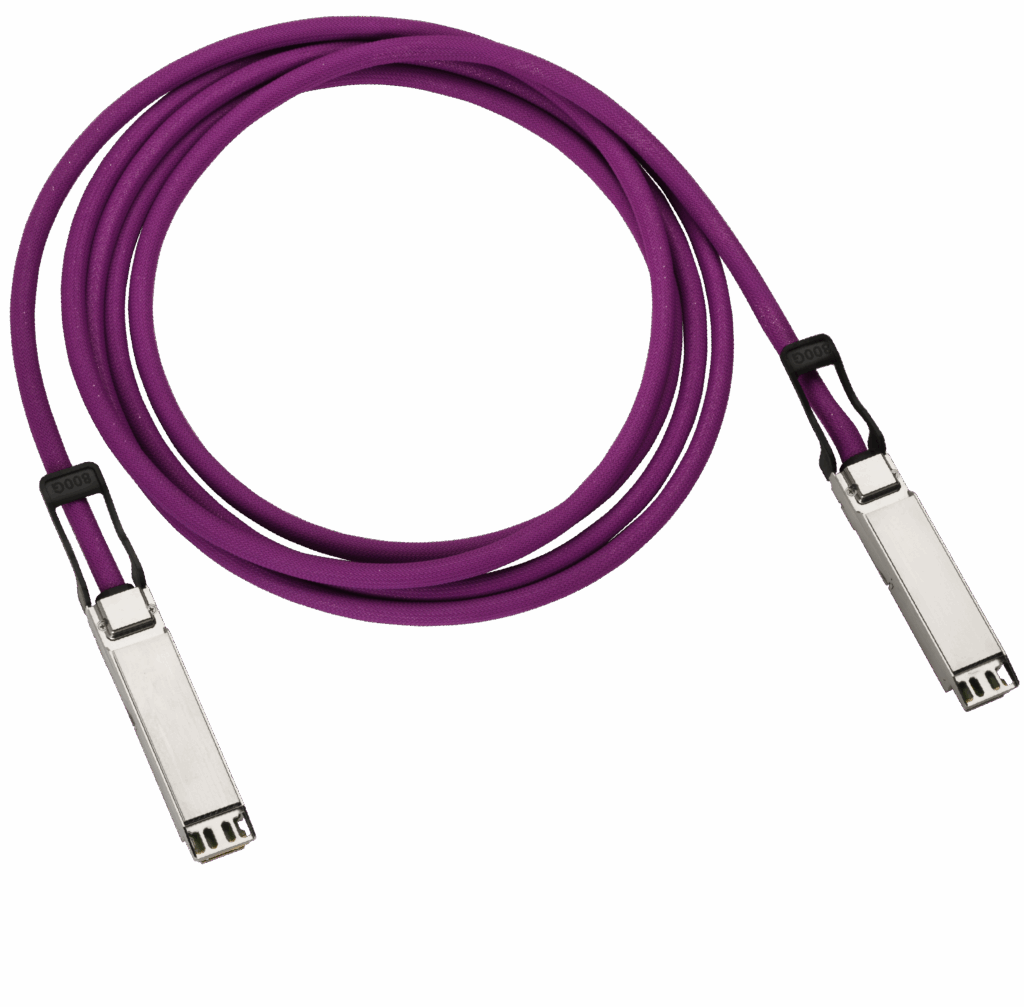

Our reliable plug-and-play copper connections are optimized for seamless operation at 100G, 200G, 400G, 800G, and 1.6T

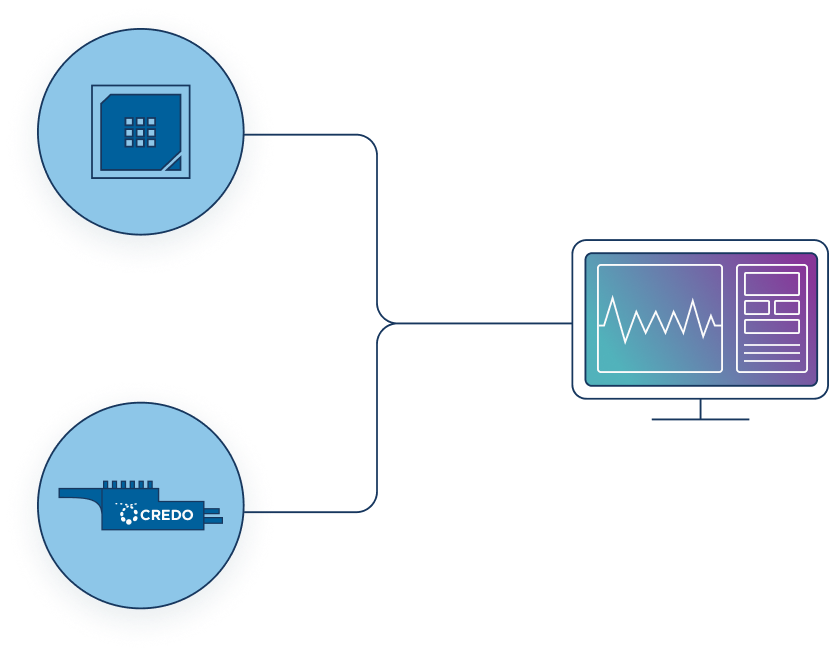

Credo invented Active Electrical Cables (AECs). These revolutionary devices enable higher speeds and longer reach than traditional direct attached cables with improved reliability, lower power consumption and seamless plug-and play capabilities.

Discover our AEC solutions

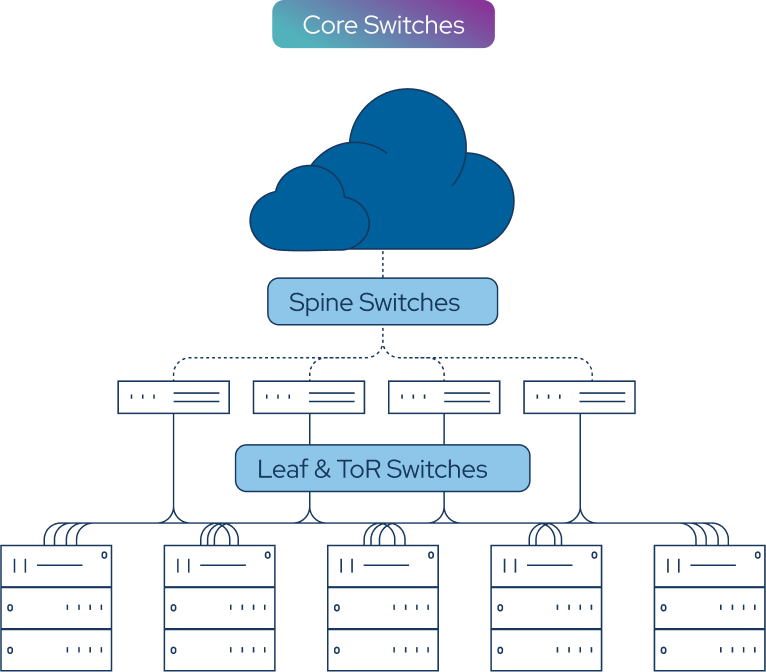

Proven performance at hyper scale

Credo connectivity solutions deliver optimized performance, reliability, energy efficiency, and security for AI deployment.

<224 G

Per lane PAM4 is essential for next-generation data centers

<88 %

AEC market share according to 650 Group

< 1.6 T

Technology is the fastest data transmission speed available

<4

Leading US hyperscalers use Credo connectivity solutions

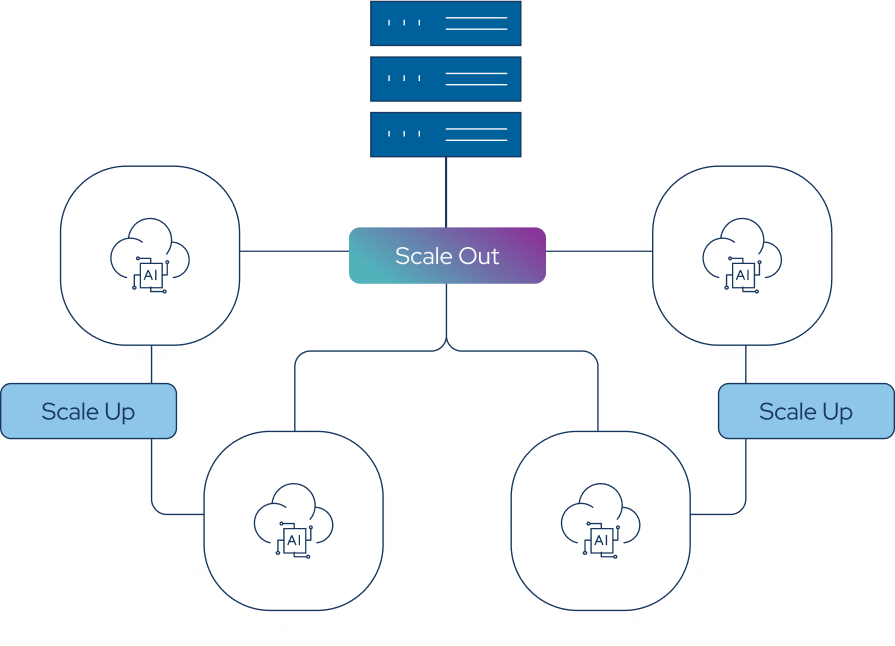

An architectural approach enabling leading-edge performance, flawless reliability, and lower power

Credo’s unique innovation framework is grounded in our core SerDes technology, advanced integrated circuit design, and system-level development approach.

About Credo

Culture of Innovation

We have an award-winning culture of innovation, collaboration and excellence.

Disrupting the Status Quo

Credo pioneered AECs – a game changer for AI cluster build-outs.

Customer-centric Approach

A systems approach of hardware + software + services enables our customers to scale.

Industry Collaboration

We help to define and shape the standards that propel the industry forward.

Supply Chain Management

The industry’s most trusted suppliers are the foundation for delivering our award-winning products.

People First

The connections our teams make have purpose with customers and partners.