Who are we?

We’re innovators, collaborators, and above all, Team Credo. For more than a decade, we’ve pushed technology forward. Our story isn’t about where we’ve been. It’s proof that believing in opportunity gives us the courage to keep breaking barriers ahead.

Credo’s Benefits and Perks

Purpose, people, and possibilities guide our employee experience.

Purpose

We invest in what matters. From meaningful-future shaping projects to competitive compensation, we empower you to grow your career while making a lasting impact. We offer:

- High-value compensation and equity packages to help you fuel your purpose outside of work too.

- Global health and wellbeing plans for all employees and their families with higher-than-industry employer contributions for non-statutory benefits.

- Professional development and tuition assistance to help you broaden your knowledge and stay current with developments in your field.

People

Connection starts within. We collaborate, celebrate wins, and create an environment where everyone can do their best work. We offer:

- Inclusive and equitable workplace standards that are reflected in both our policies and our day-to-day experiences.

- Flexible time to recharge from paid vacations, holidays, and parental leave (16-weeks in the US and statutory leave globally) plus options for other extended absences.

- On-site amenities at most office locations, from fitness centers and lactation rooms to meal options and celebrations that bring our people, their friends, and their families together.

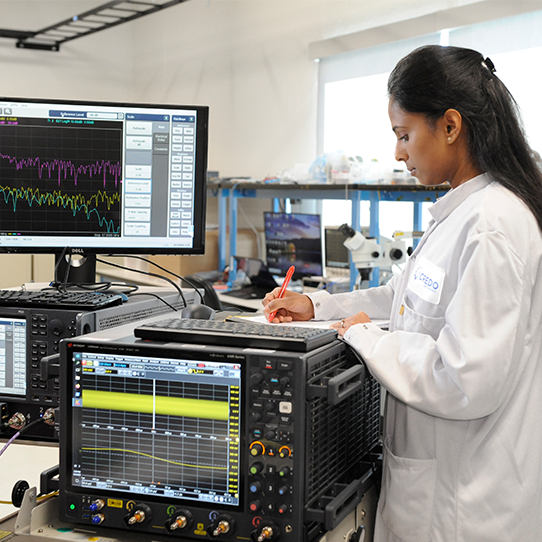

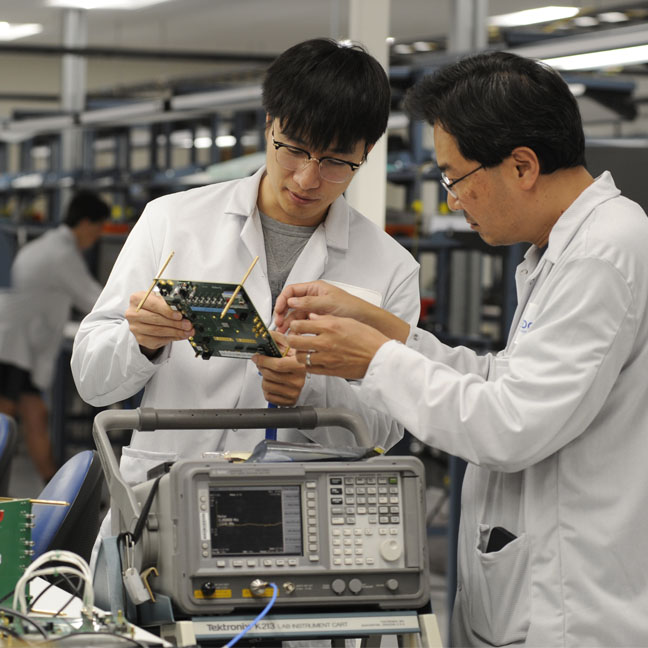

Possibilities

Our belief shapes what’s next. Credo’s technology powers the most reliable and energy-efficient connections around the world – and our team powers new products and markets that come next. We offer:

- The opportunity to shape the future of connectivity by enabling infrastructures that will underlie the next wave of AI/compute systems.

- Meaningful social responsibility with Credo Cares where you can lend your skills and create positive change in communities around the world.

- Global connections that expand your professional network as you collaborate across cultures to drive innovation.

Our Core Values

Keep learning.

Keep innovating.

We believe curiosity fuels progress. We embrace change, think critically, and push technology – and ourselves – forward.

Own the start.

Own the finish.

We believe in doing what we say we’ll do. We take challenges head-on, solve with integrity, and learn from every outcome.

Stay humble.

Stay focused.

We believe in building with purpose, not ego. We let data guide us, results define us, and progress speak for itself.

Lead with connection.

Lead with care.

We believe collaboration, respect, and fun is how great work gets done. When we operate across departments, time zones, and diverse ideas, then we operate as Team Credo.

Current job opportunities

Grow your career in a company that values innovation, impact, and inclusion. Come join our team!

|

Senior Software Application Engineer |

May 11, 2026 |

San Jose, CA |

|

|

|

About the role You will work in a fast paced, cross functional environment focused on validating high speed SerDes such as 400G, 800G, and 1.6T. The role involves electrical validation, automation development, interoperability testing, and system level debug. You’ll collaborate closely with hardware, firmware, and manufacturing teams to ensure robust performance across a variety of operating conditions. We welcome candidates with diverse backgrounds and experience levels who are passionate about high speed systems and eager to contribute to cutting edge development. Base salary range is $130,000 – $160,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Sr. Analog Design Engineer |

May 11, 2026 |

San Jose, CA |

|

|

|

About the role Credo is seeking a Sr. Analog Design Engineer for our R&D team. In this role, you will focus on IC development for our SerDes (Serializer/Deserializer) products. You will have the opportunity to work with the most advanced CMOS technology on various analog and mixed‑signal circuit blocks. The ideal candidate should have a deep understanding of analog/mixed‑signal IC design and be able to work independently. Base salary range is $120,000 to $180,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Senior Digital Design Engineer |

May 10, 2026 |

San Jose, CA |

|

|

|

About the role We’re looking for a Senior Digital Design Engineer to lead front-end ASIC design efforts, including architecture, implementation, and verification of complex logic blocks. You’ll collaborate across design, verification, and physical teams to ensure successful tape-outs, while contributing to microarchitecture specs, IP integration, and chip bring-up. This role combines technical depth with cross-functional teamwork to deliver high-performance digital solutions. Base salary range is $140,000 to $170,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Optical System Test Specialist |

May 9, 2026 |

Ottawa, Canada |

|

|

|

About the Role Credo is seeking an Optical System Test Specialist to join our Core Technology Development team in Ottawa. In this role, you will play a pivotal role in advancing optical communication products for AI infrastructures. You will collaborate closely with the R&D team, component owners and link architectures, driving innovation through system-level and component-level testing. Your expertise will be essential in evaluating the components’ performance, data analysis, ensuring integration of components toward optical links, and providing actionable feedback. This position offers a unique opportunity to work with cross-functional teams, explore new technologies, work on exciting challenges, and refine your skills. You will work on all aspects of front-end ASIC design, including project definition, micro-architecture specification, and design and verification of complex logic blocks. Additionally, you will partner with PD, DFT, STA, and PV teams to ensure successful tape-outs and work closely with system teams for chip bring-up. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Optical Packaging Designer |

May 9, 2026 |

Ottawa, Canada |

|

|

|

About the Role Credo is seeking an Optical Packaging Designer to design and develop advanced packaging solutions for photonic devices and optical components that power next-generation communication systems and high-performance computing. This is a critical technical role where you will define packaging architectures, optimize thermal and mechanical performance, and ensure reliability across diverse optical platforms. You will collaborate closely with design, R&D, and manufacturing teams to deliver robust, scalable packaging solutions for high-speed optical modules and integrated photonic circuits. This position offers a unique opportunity to influence product architecture, drive innovation in packaging technologies, and establish best-in-class practices for optical component integration. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Senior Staff Firmware Engineer |

May 9, 2026 |

San Jose, CA |

|

|

|

About the role The Senior Staff Firmware Engineer plays a pivotal role in advancing semiconductor technologies within the Firmware Engineering team. This position drives innovation in design, validation, and deployment of high-performance integrated circuits, supporting product development from concept to production while ensuring technical excellence and compliance with industry standards. Base salary range is $140,000 – $180,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Analog Engineer |

May 9, 2026 |

San Jose, CA |

|

|

|

About the role The Analog Engineer will play a critical role in connectivity technology through innovative design, development, and testing. This position offers opportunities for cross-functional collaboration in a high-tech environment, ideal for professionals passionate about microelectronics and integrated systems. The ideal candidate will have experience in one or more of the following areas: charge-pump PLL, FracN-PLL, Digital-PLL techniques, high-speed clock distribution, and high-speed digital circuit design and analysis. Base salary range is $120,000 to $140,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Senior Opto-Mechanical Engineer |

May 9, 2026 |

Ottawa, Ontario |

|

|

|

About the Role Credo is seeking a Senior Opto-Mechanical Engineer to join our Core Technology Development (CTD) team. This role is pivotal in developing innovative optical packaging solutions and scaling them for high-volume production, including test and verification. You will collaborate with a global team of experts in semiconductor micro-devices and communication systems to co-develop novel packaging concepts with vendor partners. These concepts must meet mechanical, thermal, optical, and reliability performance requirements. This is a hands-on, product development-focused engineering role ideal for someone passionate about designing high-volume systems. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Principal Optical Packaging Engineer |

May 9, 2026 |

San Jose, CA |

|

|

|

About the role Participate in the characterization and development of packaging materials and processes tailored for high-speed optical communication. This role is part of Credo’s optical communications team and focuses on enabling manufacturable, reliable, and scalable packaging solutions for next-generation optical devices. Base salary range is $190,000 to $250,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Optical DSP Application Engineer |

May 9, 2026 |

San Jose, CA |

|

|

|

About the role Fueling the next generation of AI data centers, our mission is to enable and drive high-speed communication by providing cutting-edge technology, world-class quality, and interoperability. We deliver advanced high-speed communication solutions, including chips, optical modules, and active optical cables. Our current chips support speeds up to 1.6TBps. Base salary range is $120,000 to $140,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

Extra bonus points

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Sr. Manager, ASIC Design |

May 9, 2026 |

San Jose, CA |

|

|

|

About the role As a Sr. Manager, ASIC Design, you will lead a team of engineers in delivering complex ASIC designs from specification to tape-out. This role covers all aspects of front-end ASIC design, including microarchitecture, RTL implementation, and verification of complex logic blocks. You will collaborate with PD, DFT, STA, and integration teams to ensure successful tape-outs and partner with system teams for chip bring-up and validation. Base salary range is $200,000 to $230,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Senior Technical Program Manager |

May 9, 2026 |

Ottawa, Canada |

|

|

|

About the role We are seeking a highly capable Technical Program Manager to lead our optical interconnect project in Credo Ottawa. You will coordinate multi-disciplinary R&D teams and develop detailed Gantt charts to guide the project from initial technical path development through down-selection to high-volume production. This role involves aligning priorities across teams, managing timelines and deliverables, cultivating internal and external partnerships, and assessing risk profiles at both the component and system levels to drive a clear and actionable execution plan. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Principal Product Engineer, NPI |

May 7, 2026 |

San Jose, CA |

|

|

|

About the role This role ensures that our New Product Introduction (NPI) of ALC RX component and system integration are fully characterized, verified, optimized for performance + reliability and passed on to operations team through deep technical understanding, sharp critique of supplier test data & technical explanations, technical design review, review and critique of qualification data and seamless management of component delivery for qualification, customer demo, validation and production qualification through DVT/EVT/PVT process. Base salary range is $180,000 – $250,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

Preferred Qualifications Who You Are

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Senior Application Engineer |

May 7, 2026 |

San Jose, CA |

|

|

|

About the role Team Credo is looking for a Senior Applications Engineer – Digital Signal Processing (DSP) & Communication Systems to join our Optical DSP Application Engineering team. You will play a critical role in release, validation, and system-level reliability of high-speed SerDes DSP products for next-generation AI-driven data centers and hyperscale networks. You will work across the full product stack – from hardware and firmware, to DSP algorithms and automation – while also contributing to a scalable automation and data analysis platform. Base salary range is $120,000 – $200,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Minimum Expertise – expertise in at least ONE of these areas:

Qualifications

Preferred Qualifications

Who You Are

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Sr. Director, Talent and Business Partnership |

May 7, 2026 |

San Jose, CA |

|

|

|

About the Role Credo is seeking a Sr. Director, People Talent & Business Partnership to lead an integrated people model that unifies Talent Acquisition and People Business Partnership under a single strategic leader. This role is accountable for delivering a seamless, high‑impact people experience to business leaders across the full talent lifecycle, from workforce planning and hiring through onboarding, performance, and retention. This is a senior, hands‑on leadership role for a systems‑oriented people leader who can balance strategic partnership, operational rigor, and team leadership. The senior director will serve as the single point of accountability for leader experience, while building strong recruiting and business partner capabilities that scale with Credo’s growth. Base salary range is $225,000-275,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Location: Prioritizing San Jose, CA (hybrid) This role is preferably based in San Jose in a hybrid capacity; exceptional candidates outside the area will be considered based on overall qualifications and ability to be in office on a frequent basis. Reports to: VP, People Why Credo

Key Responsibilities Integrated Leader & Customer Experience Design

Talent Acquisition Strategy & Execution

People Business Partner Leadership

Operating Model, Data & Enablement

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Optical Systems Engineer |

May 6, 2026 |

San Jose, CA |

|

|

|

About the role Team Credo is seeking an Optical Systems Engineer to help validate and optimize our next‑generation optical modules and components, supporting data rates from 50 Gbps up to 448 Gbps and beyond. In this role, you’ll use your expertise in optical systems and components to design module schematics, develop test plans, and analyze performance data to define final chip and module configurations. You’ll play a key role in ensuring our optical solutions meet the performance and reliability needs of AI, cloud, and data‑center applications. As a core member, your work will directly contribute to Credo’s leadership in high‑speed optical interconnect technologies. Base salary range is $180,000 – $210,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Sr. Director of Operations |

April 16, 2026 |

San Jose, CA |

|

|

|

About the role Team Credo is looking for a Sr. Director of Operations & Supply Chain to join our mission to transform connectivity at scale. This role will play a critical role in advancing our system designs with our many global manufacturing partners. This position offers opportunities for cross-functional collaboration in a high-tech environment, ideal for professionals passionate about manufacturing great products and developing supply chain solutions. Why Credo

Responsibilities 1. Operational Strategy & Execution

2. Leadership & Team Development

3. Process Improvement & Operational Excellence

4. Financial & Performance Management

5. Cross-Functional Collaboration

6. Risk, Compliance & Quality Management

7. Customer Experience Ownership

8. Scaling & Transformation

Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Events Marketing Specialist |

April 16, 2026 |

San Jose, CA |

|

|

|

About the role Credo is looking for a Events Marketing Specialist as part of its Marketing Communications group in San Jose. This role reports to the Vice President of Marketing Communications. You will play a key role in architecting the tradeshow experience for our key audiences, with a primary focus on marketing opportunities for our high-speed connectivity solutions. Our core customers include some of the world’s most prominent technology companies. They leverage Credo’s connectivity solutions for the AI infrastructure buildout which is changing the world. The successful candidate will provide our sales, product, PR, and IR teams with a world-class platform to engage in face-to-face meetings with their respective audiences while elevating our brand. The tradeshow specialist will also engage with other internal teams to coordinate department-specific internal events. Join us to be part of a dynamic team of marketers who are hyper-focused on moving the Credo brand forward while providing outstanding support for our sales and product teams. Base salary range is $80,000 – $120,000. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities The tradeshow and events specialist plays a key role in elevating the Credo brand through:

Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Principal Engineer |

April 16, 2026 |

San Jose, CA |

|

|

|

About the role We are seeking a Sr. Staff or Principal Engineer to join our ALC architecture team which, is responsible for ensuring that multiple optical, photonic, electronic, and mechanical components and processes will come together in a working optical datacom product. This role works closely with the NPI team to ensure that all components are fully characterized, verified, optimized for performance + reliability and passed on to operations team through deep technical understanding, sharp critique of supplier test data & technical explanations, technical design review, and evaluation of qualification data. An experienced product engineer with deep expertise in optoelectronic components and RF electronics is needed to join this team. Base salary range is $180,000 – $250,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Lead Design Specialist |

April 13, 2026 |

Ottawa, Canada |

|

|

|

About the role We are seeking an exceptional Lead ASIC Design Engineer to own the design and delivery of high-performance ICs for next-generation optical interconnect systems. This is a hands-on technical leadership role for a proven expert in analog, RF, and mixed-signal design who can operate at both the architecture and transistor level. You will lead a team of designers, drive execution from concept through silicon, and play a critical role in integrating electronic and photonic systems. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Test Specialist |

April 13, 2026 |

Ottawa, Canada |

|

|

|

About the role We are seeking a highly capable ASIC Test Specialist to support the validation and characterization of high-performance ICs for next-generation optical interconnect systems. In this role, you will be responsible for developing and executing test methodologies for analog, RF, and mixed-signal ASICs, with a focus on active optical links and transceiver chips. You will work closely with design and system teams to ensure accurate performance evaluation, debug issues, and enable successful silicon bring-up. This is a hands-on role requiring strong experience with lab instrumentation, chip-level measurements, and data analysis. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Sales Director |

March 30, 2026 |

San Jose, CA |

|

|

|

About the role Credo is seeking a Sales Director to lead engagement with a select group of Neocloud and Enterprise customers driving the next generation of AI infrastructure. This role is responsible for advancing adoption of Credo’s high speed connectivity and optical solutions across rack scale, scale up, and scale out system architectures. The position requires deep engagement at both the executive and architectural levels, influencing long-term platform decisions. As the primary owner of assigned accounts, you will align customer roadmaps with Credo’s technology strategy while orchestrating cross functional execution from early engagement through production. This role plays a critical part in expanding Credo’s footprint within the fastest growing segment of the AI market. Base salary range is $180,000 – $238,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for to earn additional compensation through Management By Objectives (MBO), equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Sr. Systems Engineer |

March 30, 2026 |

San Jose, CA |

|

|

|

About the role We are seeking a highly motivated Senior Systems Engineer to contribute to our IT infrastructure operations. This role serves as the primary technical authority and escalation point for company-wide server and infrastructure operations, accountable for reliability, scalability, security, and cost efficiency across the enterprise. The Senior Systems Engineer will be responsible for the architecture, deployment, maintenance, and ongoing optimization of our systems. As a key member of the IT team, this role will actively contribute to technical decisions and the overall direction of our infrastructure strategy. Base salary range is $120,000 – $150,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Sales Director |

March 26, 2026 |

Austin, TX |

|

|

|

About the role Credo is seeking an experienced Director of Sales based in Austin, TX to lead and expand our NeoCloud and enterprise OEM business across key strategic accounts including HPE, Dell, Lenovo, and IBM. This role is responsible for driving design-ins and revenue growth across Credo portfolio of high-speed connectivity solutions supporting next-generation AI data center deployments. The ideal candidate brings deep enterprise sales leadership experience, strong executive relationships, and the ability to influence platform decisions early in the architecture cycle. Base salary range is $180,000 – $220,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for to earn additional compensation through Management By Objectives (MBO), equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Sr. Director, Financial Information Systems |

March 26, 2026 |

San Jose, CA |

|

|

|

About the role Senior Director of Finance Information Systems is responsible for the strategic vision, implementation, and operational management of an organization’s financial technology ecosystem. This position bridges the gap between Finance and IT, ensuring that software systems such as ERPs, consolidation tools, and BI platforms accurately support real-time data for critical executive decision-making and regulatory compliance. Base salary range is $230,000 – $280,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities Application Strategy & Ownership

Strategy & Roadmapping

Partner to Finance, Supply Chain and Sales/marketing

Operations & Governance

Team Leadership & Development

Qualifications

Key Skills for Success

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Program Manager |

March 19, 2026 |

San Jose, CA |

|

|

|

About the Role Credo is seeking a self-driven, Program Manager to join our talented team. The ideal candidate will have proven ability to strategize and implement high-level program initiatives. This individual will manage multiple high-speed Serdes projects to ensure they align effectively with the company’s mission and the program’s goals. Base salary range is $110,000 – $170,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Office Assistant |

March 18, 2026 |

San Jose, CA |

|

|

|

About the role Base salary range is $22 – $28 per hour. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

About Credo Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

|

Sr. Design Verification Engineer |

February 17, 2026 |

San Jose, CA |

|

|

|

About the role Team Credo is seeking a Senior Design Verification Engineer to ensure the quality and performance of complex digital designs through rigorous verification. You’ll develop and execute verification plans, build scalable reusable testbenches, write SV‑UVM sequences, debug issues, and collaborate closely with RTL designers and firmware/application engineering teams. Base salary range is $130,000 – $160,000 a year. The base salary offer will depend on factors such as education, experience, training, skills, qualifications, and location. This position is also eligible for a discretionary bonus, equity and a full range of medical and other benefits. Why Credo

Responsibilities

Qualifications

Preferred Qualifications

About Credo Credo’s mission is to transform connectivity at scale through fast, reliable, and energy-efficient system solutions. Our high-speed copper and optical interconnect products deliver industry-leading power and performance at up to 1.6T to meet the ever-expanding data infrastructure demands of AI. Our product portfolio includes ZeroFlap (ZF) Active Electrical Cables (AECs) and ZF optical transceivers, OmniConnect memory solutions, and a suite of retimers and DSPs for optical and copper Ethernet and PCIe, all leveraging the PILOT diagnostic and analytics software platform. Credo innovations enable our customers to connect the systems that connect the world. Credo is committed to creating an inclusive environment for all employees and welcome applicants from diverse backgrounds without regard to race, color, religion, gender, sex, sexual orientation, national origin, genetic information, age, disability, veteran status, or any other legally protected basis. If you have a disability or special need that requires accommodation to navigate our website or complete the application process, email people@credosemi.com. |

||||

Our Global Team